### Simulink® Design Verifier™ Release Notes

# MATLAB&SIMULINK®

#### **How to Contact MathWorks**

Latest news: www.mathworks.com

Sales and services: www.mathworks.com/sales\_and\_services

User community: www.mathworks.com/matlabcentral

Technical support: www.mathworks.com/support/contact\_us

**T**

Phone: 508-647-7000

The MathWorks, Inc. 1 Apple Hill Drive Natick, MA 01760-2098

Simulink<sup>®</sup> Design Verifier<sup>™</sup> Release Notes

© COPYRIGHT 2007-2021 by The MathWorks, Inc.

The software described in this document is furnished under a license agreement. The software may be used or copied only under the terms of the license agreement. No part of this manual may be photocopied or reproduced in any form without prior written consent from The MathWorks, Inc.

FEDERAL ACQUISITION: This provision applies to all acquisitions of the Program and Documentation by, for, or through the federal government of the United States. By accepting delivery of the Program or Documentation, the government hereby agrees that this software or documentation qualifies as commercial computer software or commercial computer software documentation as such terms are used or defined in FAR 12.212, DFARS Part 227.72, and DFARS 252.227-7014. Accordingly, the terms and conditions of this Agreement and only those rights specified in this Agreement, shall pertain to and govern the use, modification, reproduction, release, performance, display, and disclosure of the Program and Documentation by the federal government (or other entity acquiring for or through the federal government) and shall supersede any conflicting contractual terms or conditions. If this License fails to meet the government's needs or is inconsistent in any respect with federal procurement law, the government agrees to return the Program and Documentation, unused, to The MathWorks, Inc.

#### **Trademarks**

MATLAB and Simulink are registered trademarks of The MathWorks, Inc. See www.mathworks.com/trademarks for a list of additional trademarks. Other product or brand names may be trademarks or registered trademarks of their respective holders.

#### Patents

MathWorks products are protected by one or more U.S. patents. Please see www.mathworks.com/patents for more information.

## Contents

#### R2021a

| Observer Reference block supported in Simulink Design Verifier analysis                   | 1-2 |

|-------------------------------------------------------------------------------------------|-----|

| Use Enhanced MCDC in back-to-back test generation                                         | 1-2 |

| Tuning of struct or bus parameters                                                        | 1-2 |

| Reporting enhancements for Simulink Design Verifier                                       | 1-3 |

| Streamline data dictionary workflows                                                      | 1-3 |

| Support for row-major array layout                                                        | 1-3 |

| Analyze models with Initialize Function and Terminate Function blocks                     | 1-3 |

| Analyze models that initialize with signal objects                                        | 1-4 |

| Improved analysis time performance                                                        | 1-4 |

| Improved performance and precision in design error detection                              | 1-4 |

| New option for ignoring volatile qualifier                                                | 1-4 |

| Simulink Test integration: Export test cases in Excel format                              | 1-4 |

| Analyze Model block                                                                       | 1-4 |

| Inspect enhanced MCDC objectives generated by Simulink Design Verifier using Model Slicer | 1-5 |

| Functionality being removed                                                               | 1-5 |

| Configurable Subsystem block can no longer be added to replacement model                  | 1-5 |

| R202                                                                                      | 20b |

| System object analysis                                                                    | 2-2 |

| Detect violations of high-integrity systems modeling guidelines                                 | 2-2  |

|-------------------------------------------------------------------------------------------------|------|

| Test case generation: Simplified parameters, progress indicators, and additional report details | 2-2  |

| Usability improvements for dead logic detection                                                 | 2-3  |

| R20                                                                                             | )20a |

| Design error detection for specified block input range violations                               | 3-2  |

| Validate test cases or counterexamples in parallel for faster simulations                       | 3-2  |

| Improved reporting to capture dead logic causes                                                 | 3-2  |

| Improved performance for missing coverage workflows                                             | 3-2  |

| Analyze models that contain bus element port blocks                                             | 3-3  |

| Support for C Function blocks                                                                   | 3-3  |

| Analyze models that contain instance-specific parameters                                        | 3-3  |

| Support for Stateflow Variants                                                                  | 3-3  |

| R20                                                                                             | 19b  |

| Detect data store memory access violations                                                      | 4-2  |

| Enable justification capability in design error detection analysis                              | 4-2  |

| Detect design errors in custom code                                                             | 4-3  |

| Share model representation cache files for faster analysis                                      | 4-3  |

| Debug property proving violations using Model Slicer                                            | 4-3  |

| Enable test case extension in the presence of parameter configurations                          | 4-3  |

| Run dead logic analysis in conjunction with other design error checks                           | 4-3  |

| Support for complex data type                                                                   | 4-3  |

| R20                                                                                                                                          | 19a |

|----------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Test generation for enhanced MCDC objectives                                                                                                 | 5-2 |

| Default Auto test case generation strategy                                                                                                   | 5-2 |

| Performance improvement by reusing the model representation                                                                                  | 5-2 |

| Signal Editor block source for test harness models                                                                                           | 5-3 |

| Model Slicer moves to Simulink Check                                                                                                         | 5-3 |

| Improved performance for test case extension workflows                                                                                       | 5-3 |

| Simulink Design Verifier contextual tabs in the Simulink Toolstrip                                                                           | 5-3 |

| R20:                                                                                                                                         | 18b |

|                                                                                                                                              |     |

| Floating-Point Design Error Detection: Detect occurrences of non-finite, NaN, and subnormal floating-point values                            | 6-2 |

| Stateflow Custom Code Support: Analyze and generate tests for C/C++ constructs within Stateflow charts                                       | 6-2 |

| C Caller Block Support: Analyze and generate tests for C/C++ code in blocks                                                                  | 6-2 |

| Improved Floating-Point Analysis: Reduce rational approximation for models containing single- and double-precision floating-point arithmetic | 6-2 |

| Export-Function Model Support: Analyze and generate tests for models by automatically creating schedulers that invoke model functions        | 6-2 |

| Model Slicer: Leverage fast restart to streamline model debugging workflows                                                                  | 6-3 |

| Model Slicer: Highlight and generate slice for subsystem bus interfaces                                                                      | 6-3 |

| Enhance Model Coverage of Models from Previous Releases                                                                                      | 6-3 |

| Improved Reporting for Test Generation and Dead Logic Analysis Results                                                                       | 6-3 |

Simulink Design Verifier contextual tabs in the Simulink Toolstrip . . . .

**4-3**

| Incremental Test Generation for Generated Code: Generate additional tests from within the Test Manager to increase coverage of code generated by Embedded Coder                                                                                                                                                                                                                                                                                                                                             | 7-2                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| Dead Logic Refinement for Model Slicer: Improve model slice generation by using static analysis                                                                                                                                                                                                                                                                                                                                                                                                             | 7-2                      |

| Export-Function Models: Analyze export-function models driven by scheduler                                                                                                                                                                                                                                                                                                                                                                                                                                  | 7-2                      |

| Precision Improvements: Reduce rational approximations for model analysis                                                                                                                                                                                                                                                                                                                                                                                                                                   | 7-2                      |

| Test Generation: Avoid run-time errors by using test case refinement                                                                                                                                                                                                                                                                                                                                                                                                                                        | 7-2                      |

| Minimum and maximum constraints specified on unused input signals                                                                                                                                                                                                                                                                                                                                                                                                                                           | 7-3                      |

| Lookup Tables: Use enumerated data types                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 7-3                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 17h                      |

| R20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 17b                      |

| Model Slicer: Investigate and refine active slice-time windows with the Model Slicer Data Inspector                                                                                                                                                                                                                                                                                                                                                                                                         | 17b<br>8-2               |

| Model Slicer: Investigate and refine active slice-time windows with the Model Slicer Data Inspector                                                                                                                                                                                                                                                                                                                                                                                                         |                          |

| Model Slicer: Investigate and refine active slice-time windows with the Model Slicer Data Inspector                                                                                                                                                                                                                                                                                                                                                                                                         | 8-2                      |

| Model Slicer: Investigate and refine active slice-time windows with the Model Slicer Data Inspector                                                                                                                                                                                                                                                                                                                                                                                                         | 8-2                      |

| Model Slicer: Investigate and refine active slice-time windows with the Model Slicer Data Inspector                                                                                                                                                                                                                                                                                                                                                                                                         | 8-2<br>8-2<br>8-3        |

| Model Slicer: Investigate and refine active slice-time windows with the Model Slicer Data Inspector  Modeling Support for Secure Coding Standards: Check model for compliance with secure coding requirements in CERT C, CWE, ISO/IEC TS 17961 standards to improve security of generated code  Multiword Support: Analyze models containing multiword fixed-point data types up to 128 bits  Side-Effect-Free Behavior for Design Error Detection Checks                                                   | 8-2<br>8-3<br>8-3        |

| Model Slicer: Investigate and refine active slice-time windows with the Model Slicer Data Inspector  Modeling Support for Secure Coding Standards: Check model for compliance with secure coding requirements in CERT C, CWE, ISO/IEC TS 17961 standards to improve security of generated code  Multiword Support: Analyze models containing multiword fixed-point data types up to 128 bits  Side-Effect-Free Behavior for Design Error Detection Checks  Result highlighting on the model during analysis | 8-2<br>8-3<br>8-3<br>8-4 |

| Activity-Based Time Slicing: Visualize the effect of state activity timing on Model Slicer highlighting for simulations                                                                                                                                                                                                                                                                                                                                                | 9-2                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| Bus Element Port Support: Detect design errors, generate tests, and prove properties for models containing Bus Element ports                                                                                                                                                                                                                                                                                                                                           | 9-2                  |

| Incremental Test Generation: Generate additional tests from within the Test Manager to increase coverage                                                                                                                                                                                                                                                                                                                                                               | 9-2                  |

| Improved Analysis Startup Time: Continue analysis after compatibility check                                                                                                                                                                                                                                                                                                                                                                                            | 9-2                  |

| Use Subsystem Inport and Outport blocks as starting points for Model Slicer                                                                                                                                                                                                                                                                                                                                                                                            | 9-2                  |

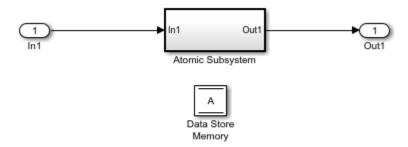

| Refined sldvextract behavior for models with Data Store Memory blocks                                                                                                                                                                                                                                                                                                                                                                                                  | 9-2                  |

| Interpret verify() statements as proof objectives for Simulink Design Verifier analysis                                                                                                                                                                                                                                                                                                                                                                                | 9-5                  |

| Respect the value of the Simulink Verification and Validation CovLogicBlockShortCircuit model parameter during Simulink Design Verifier analysis                                                                                                                                                                                                                                                                                                                       | 9-5                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                      |

| R20                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 16b                  |

| Model Slicer for Stateflow: Highlight active states and transitions for specified simulation time window                                                                                                                                                                                                                                                                                                                                                               | 16b                  |

| Model Slicer for Stateflow: Highlight active states and transitions for                                                                                                                                                                                                                                                                                                                                                                                                |                      |

| Model Slicer for Stateflow: Highlight active states and transitions for specified simulation time window                                                                                                                                                                                                                                                                                                                                                               | 10-2                 |

| Model Slicer for Stateflow: Highlight active states and transitions for specified simulation time window                                                                                                                                                                                                                                                                                                                                                               | 10-2<br>10-2         |

| Model Slicer for Stateflow: Highlight active states and transitions for specified simulation time window                                                                                                                                                                                                                                                                                                                                                               | 10-2<br>10-2<br>10-2 |

| Model Slicer for Stateflow: Highlight active states and transitions for specified simulation time window  Model Slicer: Highlight unexpected behavior in test harnesses created by Simulink Test  MCDC Test Generation: Generate tests from MCDC coverage for cascaded Simulink logic blocks  Incremental Test Generation: Generate tests to increase coverage for model objects in a test harness  Dead Logic Detection: Precisely detect dead logic without rational | 10-2<br>10-2<br>10-2 |

| <b>Analyze Models that Cont</b>                     | ain Cell Arrays                                                          | 0-3      |

|-----------------------------------------------------|--------------------------------------------------------------------------|----------|

|                                                     | ithout Floating-Point to Rational Number ion or While Loop Approximation | 0-3      |

|                                                     | R201                                                                     | 6a       |

| Test Generation: Automat                            | ically generate tests for C/C++ S-Functions                              |          |

|                                                     | v 3                                                                      | 1-2      |

|                                                     | w adjustment without the need to rerun1                                  | 1-2      |

|                                                     | liced models based on active variant1                                    | 1-2      |

|                                                     | matically find overflow errors for fixed-point word length               | 1-2      |

|                                                     | orm verification of models that contain Simulink                         | 1-2      |

| Report Generation: Gener                            | rate analysis reports in PDF format 1                                    | 1-2      |

| Model Slicer: Slice by using simulation time window | <u> </u>                                                                 | 1-2      |

|                                                     | root-level inports as starting points for 1                              | 1-3      |

|                                                     | R2015aS                                                                  | P1       |

| Bug Fixes                                           |                                                                          |          |

|                                                     | D004                                                                     | _,       |

|                                                     | R201                                                                     | <b>D</b> |

| Analysis of C S-functions                           |                                                                          | 3-2      |

| Model Slicer API                                    |                                                                          | 3-2      |

| Analyze minimum and ma                              | ximum ranges specified for bus elements 1                                | 3-2      |

| Model Advisor checks for design error detection                                                         | 13-2 |

|---------------------------------------------------------------------------------------------------------|------|

| Test Generation Advisor improvements                                                                    | 13-2 |

| Generate test inputs and export them to test cases in Simulink Test                                     | 13-2 |

| Support for Discrete Filter Blocks and Discrete Transfer Fcn Blocks                                     | 13-2 |

| R20                                                                                                     | 015a |

| Isolate important model content and reduce model complexity based on design interests with Model Slicer | 14-2 |

| Load results from previous Test Generation Advisor analysis                                             | 14-2 |

| "Parameter table" replaces "Parameter configuration table"                                              | 14-2 |

| R20                                                                                                     | 014b |

| Test generation for relational boundary values                                                          | 15-2 |

| Fast dead logic detection and Model Advisor check                                                       | 15-2 |

| Analysis for arrays of buses, For Each block, and For Each Subsystem block                              | 15-2 |

| Test Generation Advisor to guide component analysis                                                     | 15-3 |

| Improved test generation performance for lookup tables and timers                                       | 15-3 |

| R20                                                                                                     | 014a |

| Parameter Configuration Table for constraint specification and management                               | 16-2 |

| Compatibility check integrated with Model Advisor                                                       | 16-2 |

| Condition coverage test generation for Relational Operator blocks                                       | 16-2 |

| For Each Subsystem block analysis                                                                       | 16-2 |

| Parameter handling for Simulink data dictionary                                                         | 16-2 |

| R2                                                                                | 013b  |

|-----------------------------------------------------------------------------------|-------|

| Highlighting of partial results in model during analysis for visualizing progress | 17-2  |

| Summarizing and highlighting of prior analysis results                            | 17-2  |

| Performance improvements for test generation with input constraints               | 17-2  |

| Analysis time information for objectives in results window, report, and data file | 17-2  |

| Mac i64 support                                                                   | 17-2  |

| Improved while loop bound detection                                               | 17-2  |

| Internationalization support for Simulink Design Verifier Options pane            | 17-3  |

| Additional status information for undecided objectives                            | 17-3  |

| Example of property proving using Truth Table                                     | 17-3  |

| Continuous state-space block family not stubbable                                 | 17-4  |

| R2                                                                                | 2013a |

| Detection of out-of-bound array access design errors                              | 18-2  |

| R2                                                                                | 012b  |

| Support for Discrete Filter Blocks and Discrete Transfer Fcn Blocks               | 19-2  |

Japanese language localization support .....

**16-2**

| Design Error Detection For Dead Logic                             | 20-2 |

|-------------------------------------------------------------------|------|

| Filtering Model Objects From Model Coverage                       | 20-2 |

| Improved Property Proving For Look-Up Tables                      | 20-2 |

| R201                                                              | l1b+ |

| sldvtimer Function Available For Generating Test Cases            | 21-2 |

| R2                                                                | 011b |

|                                                                   |      |

| Checking Specified Design Minimum and Maximum Values              | 22-2 |

| Improved Support for Trigonometric Functions                      | 22-2 |

| Improved Support for Large Lookup Tables                          | 22-2 |

| Optimized Handling for Extending Existing Test Cases              | 22-2 |

| Support for Trigger and Enable Ports for Model Blocks             | 22-2 |

| Changed Format for sldvruntest and sldvruncgvtest Output          | 22-2 |

| Conversion of Error and Warning Message Identifiers               | 22-3 |

| R2                                                                | 011a |

|                                                                   |      |

| Automatic Detection of Overflow and Divide-by-Zero Design Errors  | 23-2 |

| Improved Analysis Results Workflow                                | 23-2 |

| Improved Support for Nonlinear Arithmetic and Math Operations     | 23-2 |

| New Capability to Highlight Analysis Results on the Model         | 23-2 |

| New Capability to Review Model Analysis Results in Model Explorer | 23-3 |

| Support for Simulink Blocks                                                        | 23-3 |

|------------------------------------------------------------------------------------|------|

| R2010b                                                                             | SP1  |

| Bug Fixes                                                                          |      |

| R20                                                                                | )10b |

| Support for 64-Bit Windows Operating Systems                                       | 25-2 |

| New Support for Specified Input Minimum and Maximum Values as Analysis Constraints | 25-2 |

| New Built-In Support for Automating Test Execution in SIL/PIL Mode via the CGV API | 25-2 |

| New Support for Extracting and Analyzing Stateflow Atomic Subcharts                | 25-2 |

| New Capability to Eliminate Unused Signals from the Generated Harness              | 25-2 |

| Support for Simulink Blocks                                                        | 25-2 |

| sldvlogsignals Replaces sldvlogdata                                                | 25-3 |

| sldvmergeharness Replaces sldvharnessmerge                                         | 25-3 |

| R20                                                                                | )10a |

| Generate Test Cases for Missing Coverage Data                                      | 26-2 |

| sldvlogdata Function for Logging Test Cases During Simulation                      | 26-2 |

| Extend Existing Test Cases                                                         | 26-2 |

| Demo Library and Models to Support Temporal Properties Specification               | 26-2 |

| Support for Stateflow Absolute-Time Temporal Logic Operators                       | 26-3 |

23-3

| Support for Simulink Blocks | 26-3 |

|-----------------------------|------|

| Support for Simuliak blocks | 20-3 |

#### R2009bSP1

|                                                                       | R2009b |

|-----------------------------------------------------------------------|--------|

|                                                                       |        |

| New Functions for Verification Objectives and Constraints             | 28-2   |

| Support for Enumerated Signals and Parameters                         | 28-2   |

| New Option to Stop Simulation on Proof Violation                      | 28-2   |

| New sldvmakeharness Function                                          | 28-3   |

| New sldvreport Function                                               | 28-3   |

| New Support for Simulink Blocks                                       | 28-3   |

| Support for New Blocks                                                | 28-3   |

|                                                                       |        |

|                                                                       | R2009a |

|                                                                       |        |

| Automatic Stubbing for Unsupported Operations                         | 29-2   |

| Long Test Case Optimization                                           | 29-2   |

| New Support for Blocks                                                | 29-2   |

| Analyzing External Functions for Embedded MATLAB Function Block       | 20.2   |

|                                                                       | 29-2   |

| Enhanced Block Replacement Capability for Subsystems and Model Blocks | 29-2   |

| New Implies Block                                                     | 29-3   |

| New Property-Proving Examples and Demos                               | 29-3   |

| sldvisactive Function                                                 | 29-3   |

| Simulink Bus Signals and Bus Objects Support       | 30-2 |

|----------------------------------------------------|------|

| Fixed-Point Data Support                           | 30-2 |

| Generating Test Harness Model with Model Reference | 30-2 |

| Generating SystemTest TEST-File                    | 30-2 |

| Improved Search Algorithms                         | 30-2 |

| New Data File Format                               | 30-2 |

| New HTML Report                                    | 30-3 |

| Blocks with No Input Ports Limitation              | 30-3 |

|                                                    |      |

| R200                                               | )8a+ |

|                                                    |      |

| Bug Fixes                                          |      |

|                                                    |      |

| R20                                                | 008a |

|                                                    |      |

| Embedded MATLAB Subset Support                     | 32-2 |

| Enhanced Support for Stateflow Truth Tables        | 32-2 |

| New Simulink Design Verifier Data File Options     | 32-2 |

| New Test Suite Optimization Setting                | 32-2 |

|                                                    |      |

| R200                                               | )7h+ |

| N200                                               |      |

|  | R20                                               |  |

|--|---------------------------------------------------|--|

|  | Fixed-Point Data Type Support                     |  |

|  | R2007a+                                           |  |

|  | Introducing the Simulink Design Verifier Software |  |

### R2021a

Version: 4.5

**New Features**

**Bug Fixes**

**Compatibility Considerations**

### Observer Reference block supported in Simulink Design Verifier analysis

You can now use the Observer Reference block to embed custom verification objectives by accessing design entities without changing the model for analysis. When analyzing models, the Observer Reference block can be used in place of the Verification Subsystem block. The Observer Reference block allows you to:

- Model design requirements as properties and prove them using Simulink<sup>®</sup> Design Verifier<sup>™</sup>.

- Establish baseline results based on the captured output, and detect model regressions.

- Generate test cases for functional design requirements using custom test objectives.

A Simulink Test<sup>™</sup> license is required to run the Simulink Design Verifier analysis on models with Observer Reference blocks. See "Access Model Data Wirelessly by Using Observers" (Simulink Test).

To use Observers, you add an Observer Reference block to your system model. The Observer Reference block houses a separate Simulink model: the Observer model. The Observer model contains Observer Ports, which are mapped to signals from your system model. To add an Observer Reference block or convert an existing Verification Subsystem block into an Observer model, see "Isolate Verification Logic with Observers".

#### Use Enhanced MCDC in back-to-back test generation

You can now generate back-to-back tests in Simulink Test that use enhanced MCDC. For more information, see "Open the Create Test for Component Wizard" (Simulink Test). In the Simulink Test Manager, click **New > Test for Model Component** in the Create Test For Model Component wizard and enable **Set Enhanced MCDC as model coverage objectives**. The new check box to use enhanced MCDC for back-to-back test generation is available only when you set **Test Input** to Design Verifier and **Simulation 2** to Simulation-In-Loop (SIL) or Processor-In-Loop (PIL). This option is in **Verification Strategy** tab. For more information, see "Create Back-to-back Tests Using Enhanced MCDC".

#### **Tuning of struct or bus parameters**

Simulink Design Verifier now supports the tuning of structures or bus parameters for all analysis modes. This allows you to:

- Tune the leaves and specify constraints of struct or a bus parameter by using the parameter table in the Configuration Parameters window or parameter configuration file.

- Simulate the model with Simulink Design Verifier generated test cases and create and run harness models with the struct or bus parameter values.

- Export the test cases generated from the analysis with the struct or bus parameter values to Simulink Test, then create and run the supported tests.

For more information, see "Specify Constraint Values for Structure or Bus Parameters".

In releases before R2021a, you cannot use sldvData that contain structure or bus parameters. You must treat these parameters as constants and then use the resultant sldvData. For more information, see "Data Types in Parameter Configurations".

#### Reporting enhancements for Simulink Design Verifier

The analysis report now includes the following additional information:

- A 128-bit checksum value for the component under test and a new function, sldvchecksum, that recalculates the checksum value

- The MATLAB® release in which the analysis has been performed

- The ability to navigate between the **Test Objectives Status** and **Test Cases** chapters

- · An objective percentage for various objective statuses

For more information about sldvchecksum, see sldvchecksum.

#### Streamline data dictionary workflows

In R2021a, you can analyze:

- The models which simultaneously access the base workspace, data dictionary, and model workspace.

- A model that has referenced models where both the top and referenced models point to different data dictionaries.

- A model with a referenced configuration set that does not contain **Design Verifier** component without making the referenced configuration set dirty. The referenced configuration set will change only if any of the options in **Design Verifier** pane of Configuration Parameters window are modified.

#### Support for row-major array layout

You can now generate tests, detect design errors, and prove properties for the models that:

- Have the model configuration parameter Array layout set to Row-major

- Have the model configuration parameter Use algorithms optimized for row-major array layout set to On

- Contain MATLAB functions that use coder.rowMajor, coder.columnMajor, coder.isRowMajor, and coder.isColumnMajor directives and checks

- Use model data elements configured to preserve array dimensions

For more information, see "Support Limitations for Simulink Software Features".

#### **Analyze models with Initialize Function and Terminate Function blocks**

You can now analyze models with Initialize Function and Terminate Function blocks. However, models with Reset Function blocks are not supported. You can use the system initialization behaviour in the Initialize Function block to check for potential design errors, verify property violations, and generate tests in the model. The behaviour captured in the Terminate Function block is ignored for Simulink Design Verifier analysis.

#### Analyze models that initialize with signal objects

You can now analyze the models that initialize using signal objects.

#### Improved analysis time performance

From 2021a, Simulink Design Verifier has reformulated analysis strategies with reduced reliance on user-specified maximum analysis time which leads to more deterministic analysis performance. You can:

- · Choose to start analysis with a high value for maximum analysis time

- Use this strategy for Design Error Detection, Auto test generation strategy and ProveWithViolationDetection property proving strategy

For more information, see sldvoptions.

#### Improved performance and precision in design error detection

In 2021a, Simulink Design Verifier has improved the performance for design error detection analysis, especially for floating-point error checks.

#### New option for ignoring volatile qualifier

Simulink Design Verifier can now ignore the *volatile* qualifier in C/C++ code. For more information, see "Handle Volatile Variables as Normal Variables".

#### Simulink Test integration: Export test cases in Excel format

Simulink Design Verifier now supports exporting test cases in Excel® format to Simulink Test Manager. Simulink Design Verifier returns those test cases in Excel and MAT format along with the harness model. You can:

- Edit the test cases in Excel format.

- Create new test cases by modifying the generated test cases.

To export the test cases from Simulink Design Verifier to Simulink Test, set **Test Data Format** to Excel in the Export Design Verifier Test Cases window. For more information, see "Export Test Cases to Simulink Test".

#### **Analyze Model block**

You can now perform analysis on the Model block. Simulink Design Verifier analyzes the Model block you select in context with the top model. You can generate tests, detect design errors, and prove properties for the Model block either from the toolstrip or by using the right-click context menu.

For example, follow these steps to generate tests for a Model block using the toolstrip:

- **1** Open the model containing Model block.

- 2 Unpin the top model in the **Analyze** menu.

- **3** Select the Model block and click on **Generate Tests** in the toolstrip.

Alternatively, right-click on the Model block and select **Design Verifier > Generate Tests for Referenced Model**. For more information, see "Generate Test Cases for Model Blocks".

### Inspect enhanced MCDC objectives generated by Simulink Design Verifier using Model Slicer

You can now launch Model Slicer for satisfied enhanced MCDC objectives to verify that the test case generated by Simulink Design Verifier impacts the detection site without being masked.

For more information, see "Inspect Enhanced MCDC Objectives using Model Slicer".

#### **Functionality being removed**

Configurable Subsystem block can no longer be added to replacement model

In Configuration Parameters, in **Design Verifier > Block Replacements**, you can no longer configure the block replacement rule to insert Configurable Subsystem blocks. The analysis will return an error if you try to specify the replacement mode as Configurable Subsystem blocks.

### R2020b

Version: 4.4

**New Features**

#### System object analysis

You can now analyze the models that contain System object™ in MATLAB System blocks and MATLAB Function blocks. You can:

- · Generate test cases for condition, decision and MCDC objectives

- Check for errors, including out-of-bound array access, division-by-zero, integer overflow, dead logic, non-finite and NaN floating-point values, subnormal floating-point values, and data store access violations

- Run property proving analysis

For more information see, Supported and Unsupported Simulink Blocks in Simulink Design Verifier.

#### Detect violations of high-integrity systems modeling guidelines

You can now detect violations of the following High-Integrity Systems Modeling (HISM) checks:

- hisl 0002: Usage of Math Function blocks (rem and reciprocal).

- hisl 0003: Usage of Square Root blocks

- hisl 0004: Usage of Math Function blocks (natural logarithm and base 10 logarithm)

- hisl 0028: Usage of Reciprocal Square Root blocks

For details, see Design Error Detection Pane Overview.

For more information about high-integrity systems modeling checks, see Model Checks for High Integrity Systems Modeling (Simulink Check).

To detect violations of HISM checks:

- 1 In the **Design Verifier** tab, in the **Mode** section, select **Design Error Detection**.

- 2 Click Error Detection Settings.

- 3 Under the **Design Error Detection** section of the **Design Verifier** configuration parameters, select the checks that you want to run in **High-Integrity Systems Modeling Checks**.

You can also detect violations of HISM checks by using the Model Advisor.

For more information on using the Model Advisor, see High Integrity System Modeling Checks (Simulink Check) and Simulink Design Verifier Checks.

### Test case generation: Simplified parameters, progress indicators, and additional report details

R2020b simplifies the options and reports for generating test cases for missing coverage.

In the Configuration Parameters dialog box, the following parameters are updated under **Design Verifier > Test Generation > Advanced Parameters > Add tests for the missing coverage**:

- **Extend using existing coverage data** Extends the coverage by generating new tests when you provide a coverage data file.

- Extend using existing test data Extends the coverage by adding new tests when you provide a

test data file.

• Separate objectives satisfied with the existing test/coverage data in the report – Impacts the reporting of the test objectives status.

The **Test Objectives Status** section of Simulink Design Verifier analysis report provides additional information for objectives satisfied with existing test or coverage data. When enabled, the **Test Objectives Status** section shows separate tables for:

- Objectives satisfied from current analysis

- Objectives satisfied using existing test or coverage data

The progress bar in the Results Summary window starts with a preloaded count of objectives satisfied by the test and coverage data and shows the progress for current analysis. The Results Summary window also includes a new status to show the objectives count satisfied by the coverage and test data.

To configure test case generation for missing coverage:

- 1 In the **Design Verifier** tab, in the **Mode** section, select **Test Generation**.

- 2 Click **Test Generation Settings**.

- 3 Under the Test Generation section of the Design Verifier configuration parameters, select Advanced Parameters.

For more information, see Design Verifier Pane: Test Generation.

#### Usability improvements for dead logic detection

R2020b simplifies the options and analysis results for dead logic detection.

- You can perform a partial check for dead logic using the **Dead logic (partial)** parameter. The

partial check does not replace an exhaustive analysis. You can run a partial check when you need

to more quickly debug errors, before investing the computing time to perform an exhaustive

analysis. To perform an exhaustive analysis, enable **Dead logic (partial)** > **Run exhaustive**analysis in the Configuration Parameters dialog box.

- The Results Summary window shows a notification when Simulink Design Verifier runs a partial check for dead logic.

- The dead logic detection reflects the validation of active logic in the Results Summary window.

To detect dead logic in your model:

- 1 In the **Design Verifier** tab, in the **Mode** section, select **Design Error Detection**.

- 2 Click Error Detection Settings.

- 3 Under the Design Error Detection section of the Design Verifier configuration parameters, select Dead logic (partial).

For more information, see Dead Logic Detection and Design Error Detection Pane Overview.

### R2020a

Version: 4.3

**New Features**

#### Design error detection for specified block input range violations

You can use design error detection analysis to detect specified input range violations for these blocks:

- · n-D Lookup Table

- · Interpolation Using Prelookup

- Prelookup

- Direct Lookup Table (n-D)

- · Multiport Switch

- Trigonometric Function, when the **Approximation method** parameter is set to CORDIC

To detect specified block input range violations in your model, on the **Design Verifier** tab, in the **Mode** section, select **Design Error Detection**. Click **Error Detection Settings**. In the Configuration Parameters dialog box, on the **Design Verifier** > **Design Error Detection** pane, select **Specified block input range violations**.

You can also detect block input range violations by using the Model Advisor. For more information, see Detect Block Input Range Violations.

### Validate test cases or counterexamples in parallel for faster simulations

If you have a Parallel Computing Toolbox™ license, you can validate test cases or counterexamples in parallel across multiple workers on the same machine for faster simulations. To enable the use of parallel computing, on the **Design Verifier** tab, in the **Prepare** section, select **Settings**. In the Configuration Parameters dialog box, on the **Design Verifier** pane, under **Advanced parameters**, select **Validate test cases or counterexamples with parallel computing**.

By default, Simulink Design Verifier uses fast restart mode to simulate the model when you use sldvruntest. To also enable the use of parallel computing for faster simulations, set the useParallel option in sldvruntest. For more information see, sldvruntest.

#### Improved reporting to capture dead logic causes

Simulink Design Verifier now reports possible causes for dead logic in the Results Inspector window. These causes are reported when dead logic occurs due to:

- Short-circuiting of a Logical Operator block during analysis

- Conditional execution of a block when the Conditional input branch execution (Simulink) parameter is set to  ${\bf On}$

#### Improved performance for missing coverage workflows

Simulink Design Verifier analysis performance while using existing test cases or existing coverage data is improved. In some cases, the analysis is faster and more objectives are satisfied. For more information, see Defining and Extending Existing Tests Cases and Missing Coverage in Subsystems and Model Blocks.

#### Analyze models that contain bus element port blocks

Simulink Design Verifier now supports analysis of models that contain In Bus Element and Out Bus Element blocks in top-level models. Before R2020a, analysis was only supported when the bus element port blocks were in the Subsystem block. For more information, see Simplify Subsystem and Model Interfaces with Buses (Simulink).

#### **Support for C Function blocks**

Simulink Design Verifier now supports analysis of models that contain C Function blocks.

#### Analyze models that contain instance-specific parameters

Simulink Design Verifier supports analysis of models that are configured to use instance-specific parameters for referenced models. For more information, see Parameterize a Referenced Model (Simulink).

#### **Support for Stateflow Variants**

Simulink Design Verifier supports analysis of models that contain Variant Transitions in Stateflow<sup>®</sup>. For more information, see Software Configurations Using Variant Transitions (Stateflow) documentation.

### R2019b

Version: 4.2

**New Features**

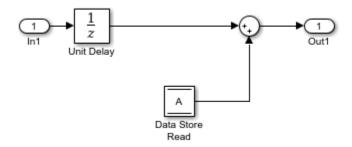

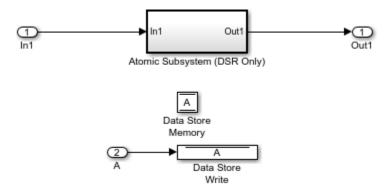

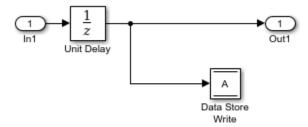

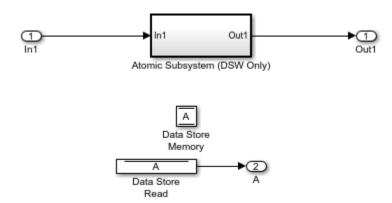

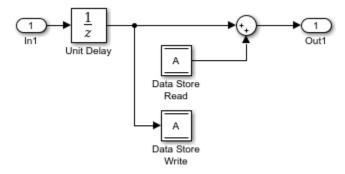

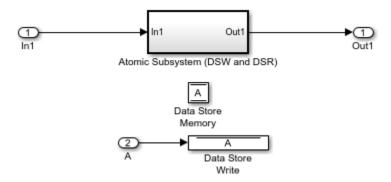

#### **Detect data store memory access violations**

In R2019b, you can use design error detection analysis to detect these access violations in Data Store Memory blocks:

- Read-before-write

- Write-after-read

- Write-after-write

To detect data store memory access violations in your model, on the **Design Verifier** tab, select **Settings**. In the Configuration Parameters dialog box, on the **Design Verifier** > **Design Error Detection** pane, select **Data store access violations**. For more information, see Detect Data Store Access Violations in a Model.

You can also detect data store access violations by using the Model Advisor. For more information, see Detect Data Store Access Violations.

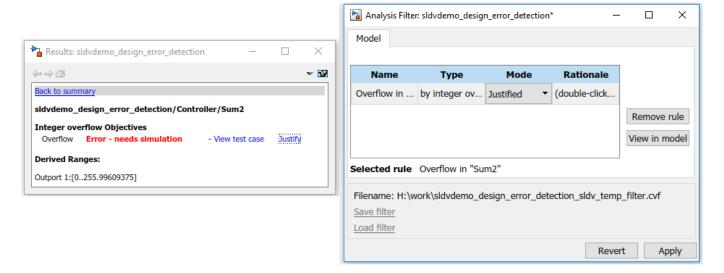

#### Enable justification capability in design error detection analysis

In R2019b, you can justify design error detection objectives by using the Analysis Filter window. To open the Analysis Filter window, after Simulink Design Verifier analysis completes, in the Results Inspector window, click **Justify**. For more information, see Filter Objectives by Using Analysis Filter Viewer.

Alternatively, you can justify objectives by using a filter file. On the **Design Verifier** tab, select **Settings**. In the Configuration Parameters dialog box, on the **Design Verifier** pane, in **Advanced parameters**, select **Ignore objectives based on filter**, then browse to the **Filter file**. For more information, see Design Verifier Pane. Before R2019b, the option **Ignore objectives based on filter** was available in Design Verifier Pane: Test Generation.

#### **Detect design errors in custom code**

Simulink Design Verifier now supports design error detection in C/C++ custom code in models and Stateflow charts. For more information, see Detect Design Errors in C/C++ Custom Code.

#### Share model representation cache files for faster analysis

In R2019b, performing Simulink Design Verifier analysis on a model creates a Simulink cache file (.slxc). For faster analysis, you can share this cache file. Simulink Design Verifier can reuse the model representation for analysis from this cache file if no changes are detected in the model. By default, the SLXC file appears in your current folder, but you can control the default location. For more information, see Share Simulink Cache File for Faster Analysis.

By default, the **Rebuild model representation** option is set to **If** change **is** detected. The analysis always reuses the model representation when no change is detected in the model. For more information, see Reuse Model Representation for Analysis.

#### Debug property proving violations using Model Slicer

You can now use Model Slicer along with Simulink Design Verifier to debug property proving violations. To launch the **Model Slicer**, open **Apps** and, under **Model Verification**, **Validation**, **and Test**, select **Design Verifier**. In the **Mode** section, select **Property Proving**, then click the **Debug with Slicer** button. For more information, see Debug Property Proving Violations by Using Model Slicer.

### Enable test case extension in the presence of parameter configurations

In R2019b, Simulink Design Verifier supports extending test cases in the presence of parameter configurations. You can apply the parameter configurations by using the parameter table or parameter configuration file. For more information see, Extend Existing Test Cases After Applying Parameter Configurations.

#### Run dead logic analysis in conjunction with other design error checks

In R2019b, you can perform dead logic analysis in conjunction with other design error checks. For more information, see Design Verifier Pane: Design Error Detection.

#### Support for complex data type

Simulink Design Verifier now supports the use of complex data types in a model for design error detection, test generation, and property proving analysis.

#### Simulink Design Verifier contextual tabs in the Simulink Toolstrip

In R2019b, the new Simulink Toolstrip includes contextual tabs for Simulink Design Verifier. To open the Simulink Design Verifier tab:

**1** Open a Simulink model.

- 2 On the **Apps** tab, click the arrow on the far right of the **Apps** section .

- 3 In the Model Verification, Validation, and Test gallery, click Design Verifier.

The following table shows the mapping from R2019a Simulink Editor to the new **Design Verifier** tab.

| R2019a Simulink Editor Menu Bar Item                                                              | Design Verifier Tab Equivalent                                                                                                            |

|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Analysis > Design Verifier > Check<br>Compatibility > Model                                       | Check Compatibility                                                                                                                       |

| Analysis > Design Verifier > Check<br>Compatibility > Enable 'Treat as Atomic Unit'<br>to Analyze | Click the Subsystem block and select Convert > Convert to Atomic Subsystem.                                                               |

| Analysis > Design Verifier > Check<br>Compatibility > Selected Subsystem                          | To check the compatibility of a Subsystem block, first convert the Subsystem block to an Atomic Subsystem.                                |

|                                                                                                   | Click the Subsystem block, then click <b>Check Compatibility</b> .                                                                        |

| Analysis > Design Verifier > Detect Design<br>Errors > Model                                      | On the <b>Design Verifier</b> tab, in the <b>Mode</b> section, select <b>Design Error Detection</b> . Click <b>Detect Design Errors</b> . |

| Analysis > Design Verifier > Detect Design<br>Errors > Selected Subsystem                         | Click the Subsystem block, then click <b>Detect Design Errors</b> .                                                                       |

| Analysis > Design Verifier > Generate Tests > Model                                               | On the <b>Design Verifier</b> tab, in the <b>Mode</b> section, select <b>Test Generation</b> . Click <b>Generate Tests</b> .              |

| Analysis > Design Verifier > Generate Tests > Selected Subsystem                                  | Click the Subsystem block, then click <b>Generate Tests</b> .                                                                             |

| Analysis > Design Verifier > Generate Tests > Advisor                                             | On the <b>Design Verifier</b> tab, in the <b>Mode</b> section, select <b>Test Generation</b> . Click <b>Advisor</b> .                     |

| Analysis > Design Verifier > Prove Properties > Model                                             | On the <b>Design Verifier</b> tab, in the <b>Mode</b> section, select <b>Property Proving</b> . Click <b>Prove Properties</b> .           |

| Analysis > Design Verifier > Prove Properties > Selected Subsystem                                | Click the Subsystem block, then click <b>Prove Properties</b> .                                                                           |

| Analysis > Design Verifier > Results > Active                                                     | On the <b>Design Verifier</b> tab, in the <b>Review Results</b> section, select <b>Results Summary</b> .                                  |

| Analysis > Design Verifier > Results > Load                                                       | On the <b>Design Verifier</b> tab, in the <b>Review Results</b> section, select <b>Load Earlier Results</b> .                             |

| Analysis > Design Verifier > Options                                                              | On the <b>Design Verifier</b> tab, in the <b>Prepare</b> section, click <b>Settings</b> .                                                 |

|                                                                                                   | The name of the <b>Settings</b> button is related to the <b>Mode</b> that you select.                                                     |

|                                                                                                   | For example, if you select <b>Test Generation</b> mode, set the analysis options by clicking <b>Test Generation Settings</b> .            |

### R2019a

Version: 4.1

**New Features**

#### Test generation for enhanced MCDC objectives

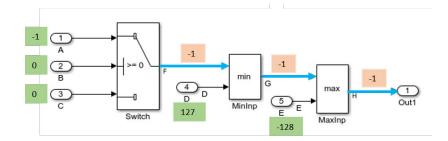

Enhanced MCDC is an extension of modified condition decision coverage. For a test block, enhanced MCDC generates test cases that avoid masking effects from downstream blocks, so that the test block has an effect on the output.

For example, a model consists of a cascade of Switch, Min, and Max blocks. The test case generated for the enhanced MCDC coverage ensures that the Switch test block is not masked by the downstream Min and Max blocks. The masking occurs if the other input to the Min block has a smaller value than the Switch output or, if the other input to the Max block has a larger value than the output of the Min block.

To generate test cases for enhanced MCDC, in the Configuration Parameters dialog box, on the **Design Verifier > Test Generation** pane, for **Model coverage objectives**, select Enhanced MCDC. Then perform test generation analysis. For more information, see Enhanced MCDC Coverage in Simulink Design Verifier.

#### **Default Auto test case generation strategy**

In R2019a, you can improve test case generation performance by using the Auto option available for the **Test suite optimization** option on the **Design Verifier** > **Test Generation** pane. By default, the test suite optimization option is set to Auto. This option adapts the analysis strategy to your model to achieve better analysis performance and precision.

The CombinedObjectives, CombinedObjectives (Nonlinear Extended), and LargeModel strategies are replaced by the Auto strategy. The LargeModel (Nonlinear Extended) option is renamed to Legacy LargeModel (Nonlinear Extended) in the **Design Verifier > Test Generation** pane. For more information, see Test suite optimization.

#### Performance improvement by reusing the model representation

Before analyzing a model, Simulink Design Verifier performs a compatibility check and saves the model representation. You can reduce the analysis time by reusing the model representation when you re-analyze the model. To reuse the representation, the model must not change, else the representation is rebuilt.

To enable the reuse of the model representation, in the Configuration Parameters dialog box, on the **Design Verifier** pane in the **Advanced parameters** section, set **Rebuild model representation** option to If change is detected. By default, the software always rebuilds the model representation during the model analysis. For more information, see Model Representation for Analysis.

The time that the software takes to build or reuse the model representation is reported in the Simulink Design Verifier reports.

#### Signal Editor block source for test harness models

Simulink Design Verifier now supports the Signal Editor block as the source block for a test harness model. With the Signal Editor block, you can create test input data scenarios and switch between the scenarios during simulation. In the Configuration Parameters dialog box, on the **Design Verifier** > **Results** pane, select Generate separate harness model after analysis. Then, select Signal Editor as the Harness source option. For more information, see Simulink Design Verifier Harness Models.

#### **Model Slicer moves to Simulink Check**

Previously, the Model Slicer was available with Simulink Design Verifier. In R2019a, the tool is available with Simulink Check™. In R2018b, you accessed the Model Slicer by selecting **Analysis > Design Verifier > Model Slicer**. In R2019a, you access the Model Slicer by selecting **Analysis > Model Slicer**. For more information on the Model Slicer, see Model Simplification with Dependency Analysis (Simulink Check).

#### Improved performance for test case extension workflows

In R2019a, test case extension analysis is improved with faster loading of existing test cases for a Simulink model that consists of input bus signals. Or, when existing test cases have repeated input values over time.

### Simulink Design Verifier contextual tabs in the Simulink Toolstrip

In R2019a, you have the option to turn on the Simulink Toolstrip. For more information, see Simulink Toolstrip Tech Preview replaces menus and toolbars in the Simulink Desktop.

The Simulink Toolstrip includes contextual tabs, which appear only when you need them. The Simulink Design Verifier contextual tabs include options for completing actions that apply only to Simulink Design Verifier.

To access the Simulink Design Verifier tab:

- 1 Open a Simulink model.

- Activate the Simulink Toolstrip by using the **Simulink Preferences**. See, Simulink Toolstrip Tech Preview replaces menus and toolbars in the Simulink Desktop.

- 3 On the MATLAB Toolstrip, from the **APPS** tab, select **Design Verifier**.

- 4 Set up Design Verifier for your analysis mode.

**5** Perform an analysis and explore the results.

### R2018b

Version: 4.0

**New Features**

#### Floating-Point Design Error Detection: Detect occurrences of nonfinite, NaN, and subnormal floating-point values

You can use design error detection analysis to detect the occurrences of non-finite, NaN, and subnormal floating-point values. To detect non-finite, NaN, and subnormal floating-point values in your model, from the Simulink Editor, select **Analysis > Design Verifier > Options**. In the Configuration Parameters dialog box, on the **Design Verifier > Design Error Detection** pane, select Non-finite and NaN floating-point values and Subnormal floating-point values.

You can also detect the floating-point values by using these Model Advisor checks:

- Detect Non-finite and NaN Floating-Point Values

- · Detect Subnormal Floating-Point Values

For more information, see Detect Non-Finite, NaN, and Subnormal Floating-Point Values.

### Stateflow Custom Code Support: Analyze and generate tests for C/C+ + constructs within Stateflow charts

Use Simulink Design Verifier to perform design error detection and property proving and generate tests for C/C++ constructs within Stateflow charts. For more information on how to enable custom code support, see Coverage for Custom C/C++ Code in Simulink Models (Simulink Coverage) and Test Generation for Custom Code in a Stateflow Chart.

### C Caller Block Support: Analyze and generate tests for C/C++ code in blocks

Use Simulink Design Verifier to perform design error detection and property proving and generate tests for the C/C++ code in C Caller blocks. For more information on how to enable custom code support, see Coverage for Custom C/C++ Code in Simulink Models (Simulink Coverage) and Test generation with a C Caller block.

# Improved Floating-Point Analysis: Reduce rational approximation for models containing single- and double-precision floating-point arithmetic

When you use Simulink Design Verifier to analyze models, Simulink Design Verifier attempts to reduce the use of rational approximation if the model uses single-precision floating-point values or double-precision floating-point values. This feature applies to all analysis modes. You can disable this feature from the Design Verifier Pane of the model configuration parameters.

For more information on how Simulink Design Verifier introduces approximations, see Floating-Point to Rational Number Conversion.

# Export-Function Model Support: Analyze and generate tests for models by automatically creating schedulers that invoke model functions

Simulink Design Verifier now supports design error detection, test generation, and property proving for export-function models. The software automatically creates schedulers that invoke the export-

function models and then perform analysis on scheduled model. For more information, see Analyze Export-Function Models.

### Model Slicer: Leverage fast restart to streamline model debugging workflows

Model Slicer now supports the model debugging workflows by using the fast restart methodology. You can use the fast restart mode to:

- Perform multiple simulations efficiently with different inputs, without recompiling the model.

- Debug a simulation by stepping through the major time steps of a simulation and inspecting how slice changes.

For more information, see Debug Slice Simulation by Using Fast Restart Mode.

### Model Slicer: Highlight and generate slice for subsystem bus interfaces

Model Slicer now supports highlighting and slice generation for models containing In Bus Element and Out Bus Element ports. You can use bus element port blocks to interface bus signals to subsystems. For more information, see Simplify Subsystem Bus Interfaces (Simulink).

#### **Enhance Model Coverage of Models from Previous Releases**

Leverage the latest release capabilities of Simulink Design Verifier on a model from a previous release. Use the workflows described in Enhance Model Coverage of Older Release Models.

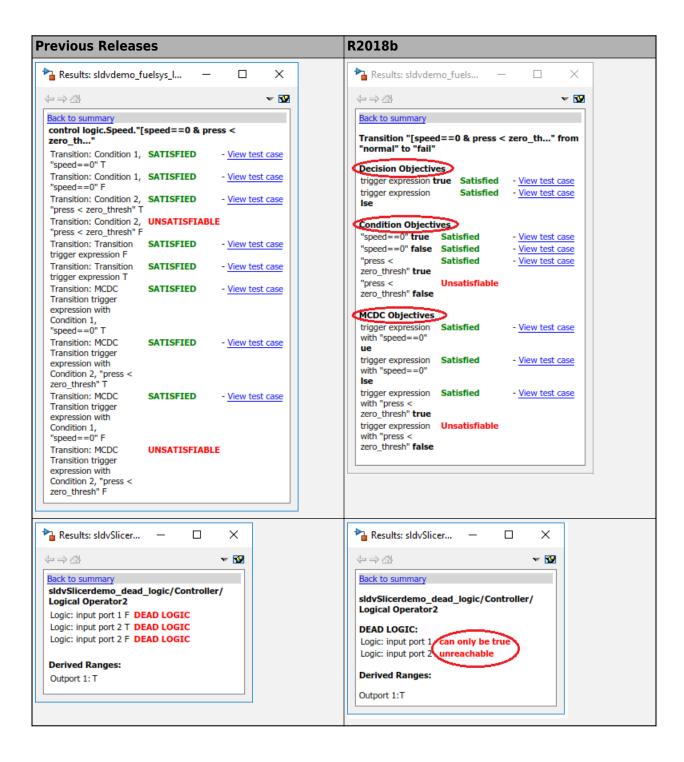

### Improved Reporting for Test Generation and Dead Logic Analysis Results

In R2018b, reporting Simulink Design Verifier analysis results in the Results Inspector window and reports is improved for better clarity and understanding.

This table shows an example of the test generation and dead logic analysis results in the Results Inspector window in previous releases and R2018b.

### R2018a

Version: 3.5

**New Features**

**Compatibility Considerations**

# Incremental Test Generation for Generated Code: Generate additional tests from within the Test Manager to increase coverage of code generated by Embedded Coder

If you have Simulink Test, you can generate tests to achieve additional coverage for code generated with Embedded Coder® from the coverage results pane in the Test Manager. After executing tests, view the cumulative coverage results in the Test Manager results pane. Select the coverage result and click **Add Tests for Missing Coverage**.

For more information, see Generate Test Cases for Embedded Coder Generated Code and Code Coverage Test Generation.

### Dead Logic Refinement for Model Slicer: Improve model slice generation by using static analysis

In R2018a, you can analyze a model slice by refining the dead logic. Use existing Simulink Design Verifier data file to highlight and refine the functional dependencies without resimulating the model. For more information, see Refine Dead Logic for Dependency Analysis.

### **Export-Function Models: Analyze export-function models driven by scheduler**

In R2018a, you can run a Simulink Design Verifier analysis on export-function models that are driven by a scheduler. For more information, see Analyze Export-Function Models.

# Precision Improvements: Reduce rational approximations for model analysis